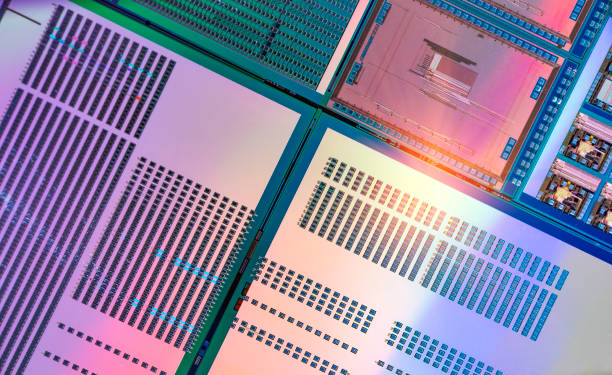

As semiconductor nodes continue to shrink, transistor architecture innovation is essential to maintain performance scaling and power efficiency. Engineers in integrated chip design are exploring advanced structures like Gate-All-Around FETs (GAAFET) and Forksheet FETs to overcome the limitations of FinFETs. These next-generation transistors promise improved electrostatic control, reduced leakage, and enhanced density, enabling the continued evolution of high-performance and low-power devices.

Structural Overview of GAAFET and Forksheet FETs

GAAFETs feature a gate that completely surrounds the transistor channel, while Forksheet FETs use separate n- and p-type channels arranged in close proximity with an insulating sheet between them. These structural differences influence transistor control, density, and manufacturing processes.

- Complete Gate Enclosure in GAAFET

The full gate wrap in GAAFETs enhances electrostatic control over the channel, minimizing short-channel effects. This structure reduces leakage and improves threshold voltage consistency, which is critical for low-power applications. - Side-by-Side Channel in Forksheet FET

Forksheet FETs place n-type and p-type channels adjacent to each other with a dielectric separator. This arrangement increases layout flexibility and enables tighter packing, improving area efficiency compared to conventional FinFETs. - Fabrication Complexity Considerations

GAAFET fabrication involves precise nanosheet stacking and alignment, demanding advanced lithography and etching techniques. Forksheet processes also require high precision but offer potential simplifications in multi-patterning steps.

Electrical Performance and Scalability

Next-generation transistor architectures directly influence device speed, power efficiency, and scalability at sub-3nm nodes.

- Enhanced Drive Current in GAAFET

GAAFETs achieve higher on-state current due to increased gate control, enhancing transistor switching speed. This leads to improved overall performance for high-speed logic and high-frequency circuits. - Reduced Capacitance in Forksheet FET

Forksheet architectures minimize parasitic capacitance between adjacent devices. Lower capacitance reduces dynamic power consumption and enables more efficient operation in densely packed circuits. - Scalability for Future Nodes

Both GAAFET and Forksheet architectures extend transistor scalability beyond FinFET limitations. Their ability to maintain performance and control at sub-3nm nodes positions them as viable options for next-generation VLSI board design.

Leakage Control and Power Efficiency

Minimizing leakage is essential in modern low-power applications, and transistor architecture plays a pivotal role in controlling subthreshold and gate leakage.

- GAAFET Leakage Reduction

The surrounding gate structure in GAAFETs significantly suppresses short-channel leakage currents. This enables lower operating voltages without compromising performance, contributing to energy-efficient designs. - Forksheet Power Management

Forksheet FETs benefit from reduced parasitic coupling between n- and p-channels, lowering standby power. Careful channel isolation and dielectric engineering ensure minimal leakage in high-density layouts. - Integration With Power Delivery Networks

Both architectures must be co-designed with power delivery considerations. Efficient power routing, voltage islands, and localized decoupling are critical to maximizing energy efficiency in advanced circuits.

Thermal Management Implications

High-density transistor layouts increase heat flux, making thermal stability a key design consideration. Proper material selection and layout strategies are critical to maintaining performance and reliability.

- Heat Dissipation in GAAFETs

Dense nanosheet stacking can increase localized thermal resistance. Optimized thermal vias and heat-spreading layers in the PCB board design help maintain safe operating temperatures and prevent thermal throttling. - Forksheet Thermal Advantage

Side-by-side channel arrangement in Forksheet FETs distributes heat more evenly, reducing hotspot formation. Coupled with advanced thermal interface materials, this architecture supports higher performance in compact layouts. - Design-Level Thermal Optimization

Collaboration between transistor design and PCB board design engineers ensures that thermal paths, vias, and copper planes are efficiently arranged to manage heat in next-generation devices.

Fabrication and Yield Considerations

Manufacturability and yield are critical for adopting new transistor architectures at scale. Both GAAFET and Forksheet FETs present unique challenges and advantages.

- Process Complexity for GAAFET

Stacking multiple nanosheets and achieving uniform gate alignment increases fabrication difficulty. Variability in sheet width and height can impact threshold voltages, requiring precise process control. - Forksheet Fabrication Flexibility

Forksheet FETs reduce the need for multiple etch steps compared to GAAFETs, potentially simplifying process flows. However, maintaining channel isolation and dielectric uniformity remains a challenge. - Impact on integrated chip design Teams

Effective collaboration with fabrication teams ensures that transistor layouts are compatible with available lithography and etching capabilities. Designers must account for process variability to maintain device performance and yield.

Applications and Design Ecosystem

Choosing the right transistor architecture depends on target applications, from mobile processors to high-performance computing. Integration into broader system designs influences architecture selection.

- High-Performance Logic Applications

GAAFETs’ superior gate control and drive current make them suitable for CPUs, GPUs, and AI accelerators requiring high speed and low leakage. - Energy-Efficient Computing

Forksheet FETs excel in dense, low-power applications where area efficiency and power reduction are paramount, such as IoT devices and mobile SoCs. - Compatibility With VLSI Board Design Practices

Both architectures must integrate seamlessly with board-level routing, signal integrity planning, and packaging strategies. Close collaboration between the transistor and VLSI board design teams ensures optimal system performance.

Design Verification and Simulation

Advanced transistor architectures demand rigorous verification to ensure functionality, performance, and reliability across all operating conditions.

- Electrical Simulation and Modeling

Accurate models of GAAFET and Forksheet FET behavior allow designers to predict drive currents, leakage, and switching speeds. Simulation tools help refine layouts and optimize transistor sizing. - Thermal and Reliability Testing

Evaluating heat dissipation and stress effects ensures long-term reliability. Design teams simulate operating conditions to prevent thermal-induced performance degradation. - Integration With PCB Board Design Validation

Co-simulating transistor performance with board-level layouts ensures that interconnects, power delivery, and signal paths do not compromise next-generation transistor benefits.

Conclusion

GAAFET and Forksheet transistor architectures represent the forefront of semiconductor innovation, offering solutions for scaling, power efficiency, and performance in sub-3nm nodes. Selecting the optimal architecture requires balancing electrostatic control, layout density, thermal performance, and fabrication feasibility. Integrating these transistors into an advanced PCB board design ensures that system-level performance, heat management, and reliability are fully realized.

Collaborative design ecosystems that merge expertise in integrated chip design, transistor fabrication, and board-level layout are essential for the successful deployment of these technologies. Companies like Tessolve bring multidisciplinary expertise across transistor design, validation, and board-level integration, supporting the development of robust, energy-efficient systems. By aligning next-generation transistor architectures with embedded system design principles and advanced board layouts, organizations can achieve high-performance, scalable, and reliable semiconductor solutions for the next decade.